# U.S. DEPARTMENT OF

Office of ENERGY EFFICIENCY & RENEWABLE ENERGY

# **Advanced Manufacturing Office**

Workshop on Ultra-Precision Control for Ultra-Efficient Devices

Workshop Report

April 21-23, 2021

Within the DOE Office of Energy Efficiency and Renewable Energy (EERE), the Advanced Manufacturing Office (AMO) collaborates with industry, small business, universities, national laboratories, state and local governments, and other stakeholders on emerging manufacturing technologies to drive U.S. industrial decarbonization, economic competitiveness, and energy productivity. AMO has a mission to develop technologies that reduce manufacturing energy intensity and industrial carbon emissions; increase the competitiveness of the U.S. manufacturing sector, with a focus on clean energy manufacturing; and reduce the life cycle energy and carbon impact of manufactured goods in the industry, buildings, transport, power, and agricultural sectors.

This document was prepared for DOE/EERE's AMO collaborative effort by DOE AMO, Boston Government Services, and Energetics Incorporated.

#### Disclaimer

This work was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or any third party's use or the results of such use of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof or its contractors or subcontractors. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof, its contractors.

## List of Acronyms

| AFM     | Atomic force microscopy                          |

|---------|--------------------------------------------------|

| AI/ML   | Artificial intelligence/machine learning         |

| ALD     | Atomic layer deposition                          |

| ALE     | Atomic layer etching                             |

| АМО     | Advanced Manufacturing Office                    |

| APAM    | Atomically precise advanced manufacturing        |

| ASD     | Area selective deposition                        |

| BEETS   | Big Energy Efficient Transistor                  |

| BJT     | Bipolar junction transistor—non-CMOS             |

| CD-SAXS | Critical dimension small-angle X-ray scattering  |

| CD-SEM  | Critical dimension scanning electron microscopy  |

| CMOS    | Complementary metal-oxide semiconductor          |

| CNT     | Carbon nanotube                                  |

| CRS     | Congressional Research Service                   |

| CVD     | Chemical vapor deposition                        |

| DOE     | Department of Energy                             |

| ECRAM   | Electrochemical random-access memory             |

| EERE    | Office of Energy Efficiency and Renewable Energy |

| EUV     | Extreme ultraviolet                              |

| FeFET   | Ferroelectric field effect transistor            |

| FET     | Field effect transistor—used in CMOS             |

| FEOL    | Front-end-of-line                                |

| FeRAM   | Ferroelectric random-access memory               |

| FIB    | Focused ion beam                                     |

|--------|------------------------------------------------------|

| GHG    | Greenhouse gas                                       |

| HDL    | Hydrogen de-passivation lithography                  |

| IC     | Integrated circuit                                   |

| ICT    | Information and communication technology             |

| ІоТ    | Internet of things                                   |

| IP     | Intellectual property                                |

| IV     | Current-voltage                                      |

| ME     | Magnetoelectric                                      |

| MEMS   | Micro-electromechanical system                       |

| MESO   | Magnetoelectric spin-orbit                           |

| MIM    | Microwave impedance microscopy                       |

| MMIC   | Monolithic microwave integrated circuit              |

| MOSFET | Metal oxide semiconductor field effect transistor    |

| MRAM   | Magnetoresistive random access memory                |

| NIST   | National Institute of Standards and Technology       |

| NSF    | National Science Foundation                          |

| РСМ    | Phase change memory                                  |

| PPACT  | Power, performance, area, cost, and time             |

| R&D    | Research and development                             |

| RDD&D  | Research, development, demonstration, and deployment |

| RF     | Radio frequency                                      |

| ROI    | Return-on-investment                                 |

| RRAM   | Resistive random-access memory                       |

|        |                                                      |

| SAXS      | Small angle X-ray scattering                                          |

|-----------|-----------------------------------------------------------------------|

| SBIR/STTR | Small business innovation research/small business technology transfer |

| SC        | Office of Science                                                     |

| SEM       | Scanning electron microscopy                                          |

| SI        | International System of Units                                         |

| SIA       | Semiconductor Industry Association                                    |

| SOI       | Silicon-on-insulator                                                  |

| SOT       | Spin orbit torque                                                     |

| SPM       | Scanning probe microscopy                                             |

| SRC       | Semiconductor Research Corporation                                    |

| STEM      | Scanning transmission electron microscopy                             |

| STM       | Scanning tunneling microscopy                                         |

| STT       | Spin transfer torque                                                  |

| TEM       | Transmission electron microscopy                                      |

| TFET      | Tunneling field-effect transistor                                     |

| UPM       | Ultra-precise manufacturing                                           |

| VLSI      | Very large-scale integration                                          |

| XRD       | X-ray diffraction                                                     |

| XRF       | X-ray fluorescence                                                    |

| XRR       | X-ray reflectometry                                                   |

### **Executive Summary**

The U.S. Department of Energy's (DOE's) Advanced Manufacturing Office (AMO) held its second virtual Workshop on Semiconductor R&D for Energy Efficiency on April 21–23, 2021. This public workshop—titled Ultra Precision Control for Ultra Efficient Devices—brought together more than 200 leading scientific and technical experts to identify opportunities to use ultra-precise manufacturing (UPM) processes and metrology and characterization tools to accelerate the development and deployment of ultra-energy-efficient devices. The workshop featured perspectives of researchers from national laboratories, universities, government agencies, and industry with expertise in devices, processes, and metrology and characterization. This workshop was intended to inform an AMO research, development, demonstration and deployment (RDD&D) plan to significantly reduce semiconductor energy use by 2030.<sup>1</sup>

The initial plenary and panel speakers clarified the strong alignment of AMO's, the office of Energy Efficiency and Renewable Energy's (EERE's), DOE's, and the federal government's RDD&D goals with the goals of the <u>semiconductor industry</u>. The semiconductor chip shortage—especially for the automotive industry—was also noted as a sign of the need for more investment in U.S. semiconductor manufacturing. After the introductory plenaries, the workshop was divided into three technical topics: ultra-energy-efficient devices, UPM processes, and UPM tools and characterization. Each technical topic included a moderated panel discussion and a facilitated session.

The following themes were emphasized during the workshop discussions:

- The need for ultra-energy-efficient semiconductor devices and processes in the next decade.

- The potential to accelerate the growth of the domestic high-tech workforce through RDD&D investments in the semiconductor industry.

- The importance of RDD&D investments in the following priority research areas, for the development of ultra-energy efficient semiconductor devices:

- Co-design

- Processes

- Materials

- Chemistry

- Metrology.

The highly interrelated nature of the workshop's three technical topics is apparent when comparing the priority research areas and their relationship to these technical topics, shown in Table ES-1. Five of the six priority research areas, described below, are directly relevant to two or more of the technical topics.

1. Co-design: extending energy-efficiency beyond the device level: Although device-level improvements are necessary for large gains in energy efficiency or other performance metrics, device-level improvements may not be sufficient to translate into increases in system-level efficiency when fully integrated. A co-design approach is necessary to ensure and maximize system-level efficiency by improving understanding of the relationship between system-level and device-level performance. Co-design is also an effective means to focus resources on innovative concepts that have the best system-level performance potential. Collaboration between researchers at different levels of the stack and those in a variety of fields will provide the diverse knowledge base needed to tackle this problem.

<sup>&</sup>lt;sup>1</sup> This workshop report summarizes the presentations, panel discussions, and facilitated discussions that took place at this event. More detailed summaries are available in the Appendix. Note that the results presented here are a snapshot of the viewpoints expressed by the experts who attended the workshop and do not necessarily reflect those of the broader device, semiconductor manufacturing, and metrology and characterization communities.

- 2. Processes: establishing a partnership-based approach to introducing ultra-precision processes: The increasing complexity of emerging ultra-efficient devices and interconnect fabrics will require ultra-precision process development to manufacture them. Contributing to this complexity are the increasing heterogeneity of materials combinations, the push towards three dimensional devices, interconnects, and their integration including, the need for ultra-precision in pattern transfer and material interfaces. Workshop participants identified collaboration with toolmakers as an essential step toward successful introduction of ultra-precision manufacturing processes at scale. This collaborative approach could be a win-win scenario where ultra-precision processes benefit the toolmakers by helping to solve their immediate problems (e.g., contact resistance) and in turn, toolmakers benefit the ultra-precision process development by helping ensure that each of the newly developed processes for ultra-efficient devices is compatible with existing manufacturing processes, especially thermal budget and potential contamination issues.

- 3. Materials: leveraging atomic precision to engineer conventional materials (rather than using new materials): Novel materials or material combinations are necessary in some of the most promising ultra-efficient devices. However, these materials face material growth and material and interfacial quality challenges that have hindered their commercialization. At the same time, contamination of existing process lines from these novel materials makes chip manufacturers hesitant to adopt these technologies. Recent advances in ultra-precision atomic manipulation to engineer materials' electronic properties suggests that some of these novel materials can be replaced with more common ones. Conventional materials have the advantages of avoiding the need for new material growth and synthesis processes and having mature, established supply chains. One critical challenge facing this approach is the severely diminished throughput for producing today's engineered materials compared with conventional growth and synthesis processes.

- 4. Chemistry: identifying promising precursors for surface chemistry-based self-assembly approaches: Many of the most scalable UPM processes that are energy efficient are bottom-up (e.g., self-assembly) approaches that rely on surface chemistry to etch, deposit, or pattern. Optimizing the complex chemical compounds (i.e., precursors) that these processes depend on can greatly enhance reaction kinetics, materials coverage, and process reliability. High throughput experimentation and machine learning (ML) can be leveraged to accelerate the discovery of promising precursors and develop scalable processes to manufacture them. If these processes can be scaled, the aforementioned technologies for engineered materials may also be needed to guide certain self-assembly processes.

- 5. Metrology: combining approaches for more energy efficient and secure metrology: As devices shrink, the number and importance of metrology steps increases, as does the importance of *decreasing process variability*. In-situ metrology helps researchers and manufacturers better understand sources of variability and better control their processes. Furthermore, most metrology and characterization methods used today rely on a modeling step for parameter estimation and understanding the underlying physics is critical to truly comprehend and make use of the measurements. Hybrid metrology, a technique where multiple tools are used, is able to further reduce uncertainties compared with model-based measurements alone. AI/ML can be leveraged with the influx of data from metrology steps to drastically reduce the data stored and transmitted and improve the energy efficiency and security of these metrology steps.

Throughout the workshop, a number of cross-cutting issues emerged. These are topics that are not strictly research focused but are included because they continued to come up in all research needs discussions. The most prevalent was limited access to facilities and equipment for academic and small business researchers, summarized below.

Access to facilities and equipment: Improving access to state-of-the-art facilities and equipment was stressed multiple times throughout the workshop. During the federal panel Q&A, Lloyd Whitman from the National Science Foundation (NSF) noted this is a significant need for academic researchers as highlighted by a recent workshop on the topic (Basu et al. 2021). In addition to academic researchers, participants noted that small business researchers also cannot access equipment at large foundries due to economics, material contamination concerns, and schedule. In addition, advanced node foundries do not currently exist in the United States. Industry-government partnerships to build and enable access to state-of-the-art semiconductor fabrication capabilities for prototyping new devices and circuit designs will accelerate progress on new device commercialization.

| Table ES-1: A crosswalk betw       | ween priority res        | earch areas and | d technical topics  |

|------------------------------------|--------------------------|-----------------|---------------------|

|                                    | Workshop Technical Topic |                 |                     |

| Priority research area             | Devices                  | Processes       | Metrology and Tools |

| Co-design                          | Х                        | Х               | Х                   |

| Processes                          | Х                        | Х               | Х                   |

| Materials                          | Х                        | Х               | Х                   |

| Chemistry                          |                          | Х               |                     |

| Metrology                          |                          | Х               | Х                   |

| Access to facilities and equipment | Х                        | Х               | Х                   |

Based on report outs and discussions on the workshop's final day the following **takeaways** emerged:

- For emerging devices, industry must be guided by a holistic set of metrics, not just energy efficiency, because customers will expect energy efficiency while also improving or at least maintaining other performance metrics of today's devices.

- The capital cost and energy consumption of semiconductor manufacturing is very high and growing rapidly.

- Development of emerging energy-efficient devices can drive the growth of U.S. semiconductor manufacturing (now 12%) to a leadership level (35%–40%).

- The domestic semiconductor industry workforce must grow if the United States is to take a leading role in semiconductor manufacturing.

- Improvements in the manufacturability of ultra-energy-efficient technologies can increase U.S. semiconductor manufacturing and the number of well-paying jobs.

- Digitalization of manufacturing (Industry 4.0) will drive a growing need for more semiconductor devices and products.

- Innovation in semiconductor manufacturing will help reach the Biden Administration's climate and energy goals (e.g., net-zero greenhouse gas emissions by 2050).

- Manufacturers will need to increase their use of semiconductors to finely control their processes as they pursue electrification for decarbonization.

- Ultra-energy-efficient technologies will enable the continued growth of our world economy without a corresponding increase in planetary energy use.

- AMO investments in UPM for transistor, memories, interconnects, and 3D integration technologies are promising and could decrease transistor use by a factor of 10.

- The U.S. manufacturing sector is more supportive of a U.S. semiconductor supply chain to prevent chip shortages that are currently slowing automotive and other manufacturing.

## **Table of Contents**

| List of Acronyms                                                                     | iii |

|--------------------------------------------------------------------------------------|-----|

| Executive Summary                                                                    | vi  |

| Table of Contents                                                                    | ix  |

| List of Figures                                                                      | x   |

| List of Tables                                                                       | xi  |

| Background                                                                           | 1   |

| Workshop Series                                                                      | 1   |

| Workshop Motivation                                                                  | 2   |

| Workshop Overview                                                                    | 3   |

| Opening Plenary Session                                                              | 4   |

| Ultra-Energy-Efficient Devices                                                       | 5   |

| Near-term Emerging Ultra-energy-efficient Devices                                    | 6   |

| Challenges and R&D Opportunities for Ultra-Efficient Devices                         | 10  |

| Ultra-precise Manufacturing Processes                                                | 13  |

| Emerging Ultra-Precise Manufacturing Processes                                       | 14  |

| Challenges and R&D Opportunities for Ultra-precise Manufacturing Processes           | 17  |

| UPM Tools and Metrology                                                              | 19  |

| Ultra-Precise Manufacturing Tools and Metrology for Ultra-Precise Manufacturing      | 20  |

| Challenges and R&D Opportunities for Ultra Precise Manufacturing Tools and Metrology | 22  |

| Non-technical Cross-Cutting Issues                                                   | 24  |

| References                                                                           | 26  |

| Appendix A: Agenda                                                                   | 29  |

| Appendix B: Plenary and Panel Talk Summaries                                         | 31  |

| Day 1                                                                                | 31  |

| Day 2                                                                                | 35  |

| Day 3                                                                                | 40  |

| Appendix C: Full Workshop Facilitation Tables                                        | 43  |

| Appendix D: Workshop Participants                                                    | 51  |

# List of Figures

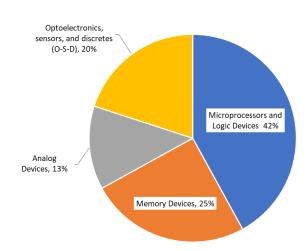

| Figure 1: Market segments of the semiconductor industry and the breakdown of sales, in percentages. Logic, memory, and RF devices, one of the primary subjects of the workshop, represent roughly 80% of the                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| semiconductor market, equating to approximately \$340 billion in sales1                                                                                                                                                                                                                                                                |

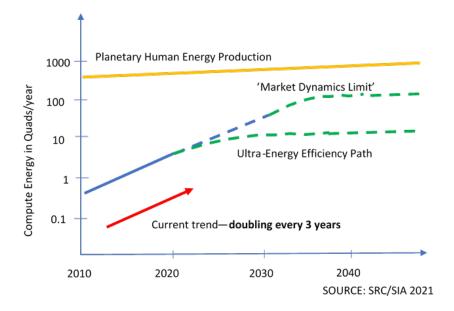

| Figure 2: At current growth rates of computational energy use, the "Market Dynamics Limit" will be reached<br>by 2035, limiting the world's computing capacity and economic growth. Alternatively, prioritizing ultra-high<br>energy efficiency in semiconductor products can achieve an 'ultra-energy-efficiency' trajectory in which |

| computing/economic growth and energy use are decoupled                                                                                                                                                                                                                                                                                 |

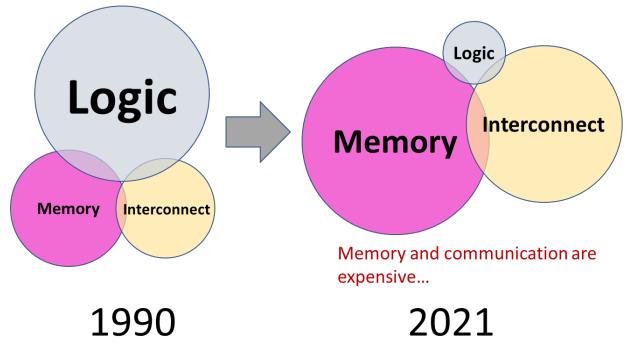

| Figure 3: Relative energy consumption of logic, memory, and interconnects in 1990 and 2021. With Moore's Law and other improvements—such as new materials and device architectures—primarily directed at logic                                                                                                                         |

| devices, energy consumption of memory and interconnects outpaced that of logic. Source: Zhirnov, V., 2021.6                                                                                                                                                                                                                            |

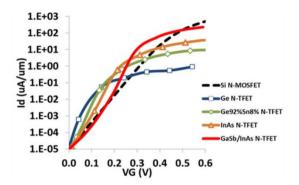

| Figure 4: All TFETs exceed the 60 mV/decade upper limit slope of MOSFET                                                                                                                                                                                                                                                                |

| (Avci, Morris, and Young 2015)                                                                                                                                                                                                                                                                                                         |

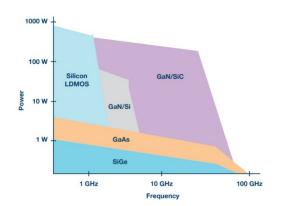

| Figure 5: GaN is able to operate at significantly higher power at similar frequencies compared with traditional                                                                                                                                                                                                                        |

| GaAs and SiGe technology (Benson 2017)                                                                                                                                                                                                                                                                                                 |

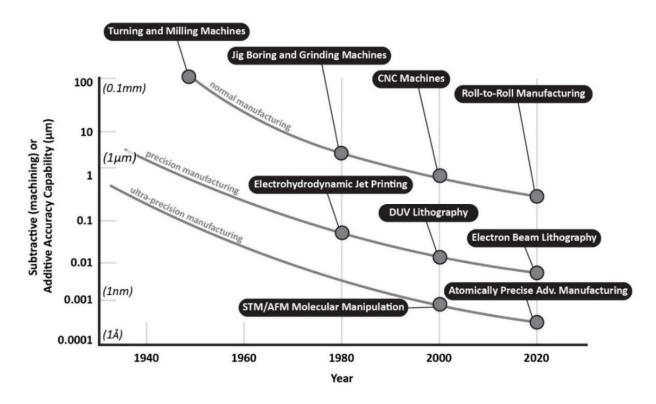

| Figure 6: An adaptation of Taniguchi's plot showing the improvements in manufacturing precision over the                                                                                                                                                                                                                               |

| 20th and 21st centuries. Modified with permission from P. Shore (Shore and Morantz 1973)                                                                                                                                                                                                                                               |

| Figure 7. Examples of block copolymers (Feng 2017)                                                                                                                                                                                                                                                                                     |

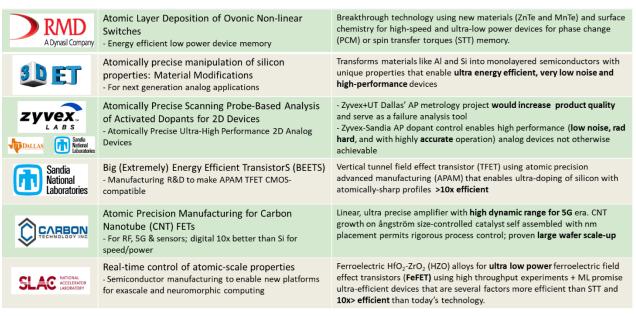

| Figure 8: Summary of AMO's APM for microelectronics program                                                                                                                                                                                                                                                                            |

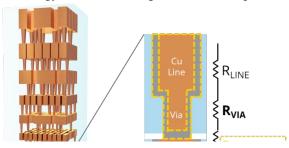

| Figure 9: Schematic of back-end metal layers. Atomically precise nucleation and termination of via fill is                                                                                                                                                                                                                             |

| critical to minimize via and interface resistance. Source: Achutharaman, R., 2021                                                                                                                                                                                                                                                      |

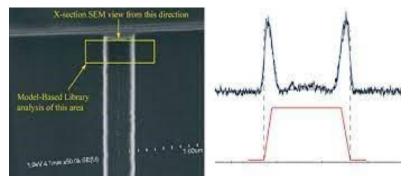

| Figure 10. CD-SEM (Villarrubia, Vladar, and Postek 2005)                                                                                                                                                                                                                                                                               |

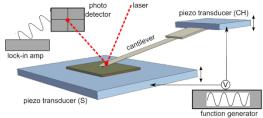

| Figure 11. Schematic of an AFM (NIST)                                                                                                                                                                                                                                                                                                  |

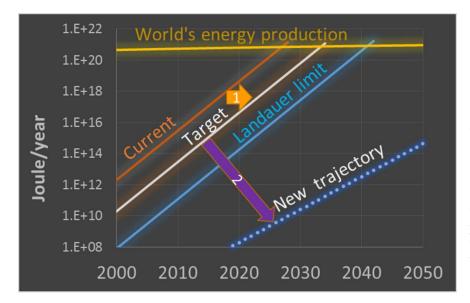

| Figure 12: Various trajectories of computational energy use. "Current," "Target," and "Landauer limit" utilize                                                                                                                                                                                                                         |

| the traditional computational paradigm, with a bit utilization of 2/3, and will hit the world's energy production                                                                                                                                                                                                                      |

| in the coming decades. Radically new computing paradigms such as quantum and neuromorphic computing                                                                                                                                                                                                                                    |

| and AI engines will push us towards the "New trajectory." Source: Zhirnov, V., 2021                                                                                                                                                                                                                                                    |

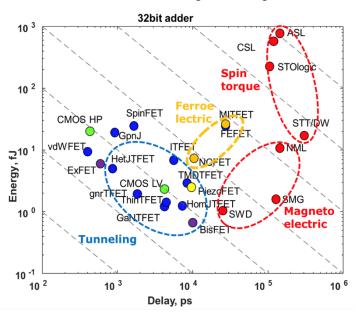

| Figure 13: Benchmarking study showing the switching energy vs delay of emerging devices, TFETs, FeFETs,                                                                                                                                                                                                                                |

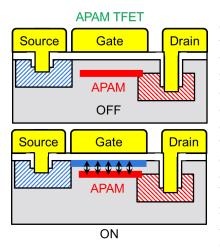

| and magneto-electric, compared with state-of-the-art silicon devices, green dots (Nikonov and Young 2015).34 Figure 14: Schematic showing the operating mechanism of the vertical TFET. Source: Lu, IEEE                                                                                                                               |

| Nanoelectronics Workshop, 2021                                                                                                                                                                                                                                                                                                         |

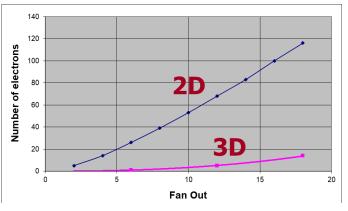

| Figure 15: 3D devices can achieve larger fan out (branching) while using a smaller number of electrons (i.e.,                                                                                                                                                                                                                          |

| energy consumption) due to its 3D architecture. A 10x energy reduction is observed in fanout of 4–6. Source:                                                                                                                                                                                                                           |

| Clark, R., 2021 (adapted from Zhirnov, Victor and Ralph Cavin. 2015. "Microsystems for Bioelectronics:                                                                                                                                                                                                                                 |

| Scaling and Performance Limits." Elsevier)                                                                                                                                                                                                                                                                                             |

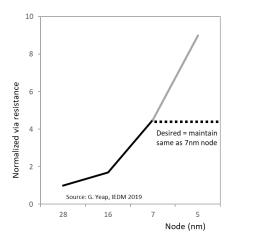

| Figure 16: Via resistance increasing dramatically as node shrinks. Source: Achutharaman, R., 2021                                                                                                                                                                                                                                      |

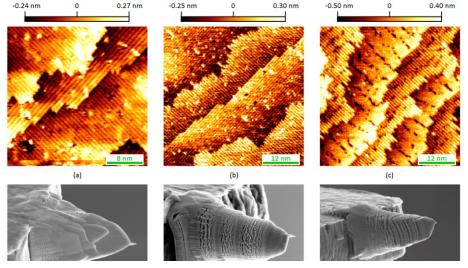

| Figure 17: Images of hydrogen terminated Si(100) acquired from three different MEMS devices. Image quality                                                                                                                                                                                                                             |

| is comparable to conventional STM. Source: Moheimani, R., 2021                                                                                                                                                                                                                                                                         |

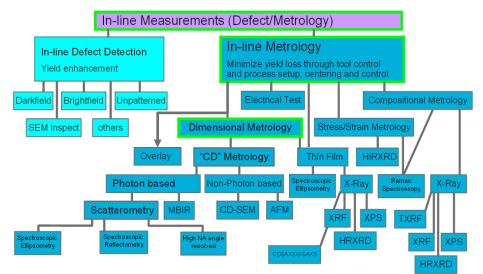

| Figure 18: A partial hierarchy of measurements showing the large number of techniques that can be used for                                                                                                                                                                                                                             |

| metrology. Source: IBM                                                                                                                                                                                                                                                                                                                 |

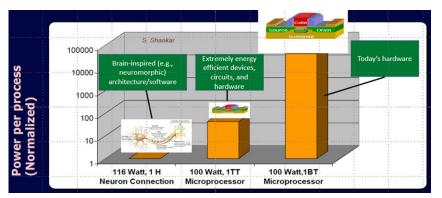

| Figure 19: Comparison of energy consumption for three systems: today's hardware, extremely energy efficient                                                                                                                                                                                                                            |

| devices, and neuronal connections. A typical microprocessor consumes roughly 10 <sup>3</sup> to 10 <sup>4</sup> more power per                                                                                                                                                                                                         |

| process than the brain. Source: Shankar, S., 2021                                                                                                                                                                                                                                                                                      |

## **List of Tables**

| Table ES-1: A crosswalk between priority research areas and technical topicsviii                         |

|----------------------------------------------------------------------------------------------------------|

| Table 1: Participant Input on Ultra-energy-efficient Devices                                             |

| Table 2: Summary of Facilitated Session on UPM Processes    19                                           |

| Table 3: Participant input on UPM Tools and Metrology                                                    |

| Table B-1: Ultra-energy-efficient Devices Report-Out (Moderator: Paul Syers, Co-chair: Alan Seabaugh)40  |

| Table B-2: Ultra-precise Manufacturing Processes Report-Out (Moderator: Tina Kaarsberg, Co-chair: John   |

| Randall)                                                                                                 |

| Table B-3: Ultra-precise Manufacturing Tools and Metrology Report-Out (Moderator: Rick Silver, Co-chair: |

| Bryan Barnes)                                                                                            |

| Table C-1: Emerging ultra-efficient devices and performance metric tradeoffs                             |

| Table C-2: Materials and design challenges and supply-constrained materials                              |

| Table C-3: R&D Pathways for Ultra-efficient Devices    45                                                |

| Table C-4: Ultra precise manufacturing processes likely to make the greatest impact on chip-level energy |

| efficiency in the next 10 years                                                                          |

| Table C-5: Scale-up and integration challenges of UPM processes    46                                    |

| Table C-6: R&D Pathways for UPM Processes                                                                |

| Table C-7: UPM metrology techniques for ultra-precise manufacturing                                      |

| Table C-8: Challenges and Barriers for UPM Tools and Metrology                                           |

| Table C-9: R&D Pathways for UPM Tools and Metrology    49                                                |

| Table C-10: Additional Cross-Cutting Issues    49                                                        |

### Background

On April 21-23, the U.S. Department of Energy's (DOE's) Advanced Manufacturing Office (AMO) within the office of Energy Efficiency and Renewable Energy (EERE) held the second in a series of workshops on different topics related to semiconductor research and development (R&D) to increase energy efficiency. This workshop focused on ultra-energy-efficient devices and the ultra-precision manufacturing (UPM) processes and next-generation control and metrology technologies needed to manufacture these devices. In addition to the industry needs and RDD&D opportunities, AMO's new goal on greenhouse gas (GHG) reduction was addressed. The output of this workshop will inform AMO's future R&D portfolio investments; provide perspectives on trends, drivers, and challenges for ultra-energy-efficient devices and enabling technologies; and help the stakeholder community understand the opportunities on the horizon.

**Workshop Series**

Semiconductors power key products that are rapidly growing in importance in all sectors of the economy, including consumer goods, finance, transportation, and manufacturing. Advances in semiconductor technology are critical for global competitiveness as well as economic, national, and climate security. According to an October 2020 Congressional Research Service (CRS) report, the global semiconductor industry in 2019 had \$424 billion in sales with the United States accounting for roughly half. The CRS divides the industry into four segments, shown in Figure 1. Because of its economic importance and the potential for its products to improve quality of life and reduce energy use in other sectors, growth of the semiconductor industry is desired; but innovation is needed to ensure this growth is accompanied by major improvements in energy efficiency. In the past, semiconductor industry and product energy use were flat or declining due to efficiency innovations. However, since 2010, as shown in Figure 2, it has begun to dramatically increase--doubling every 3 years (SIA 2019).

Figure 1: Market segments of the semiconductor industry and the breakdown of sales, in percentages. Logic, memory, and RF devices, one of the primary subjects of the workshop, represent roughly 80% of the semiconductor market, equating to approximately \$340 billion in sales.

Multiple trends in semiconductor related energy use are combining to make increased energy efficiency a top priority for the industry and the federal government.

increase the competitiveness of domestic semiconductor manufacturing, spur domestic job creation, and combat the climate crisis through reduced energy consumption across all sectors that use semiconductor technology. - Kelly Speakes-Backman,

The work that you're doing to develop ultraprecise manufacturing technologies will help

Acting Assistant Secretary, EERE

These trends include the increasing energy consumption of semiconductor manufacturing processes; the decrease in improvements in energy consumption per chip; and the acceleration of the use of microelectronics in products and processes—which, ultimately, has substantially increased the overall energy use of semiconductor industry processes and products.

A major new driver for AMO efforts with respect to semiconductor energy efficiency is the Biden Administration's goal of cutting GHG emissions by 50% by 2030 through aggressive industrial decarbonization and electrification. This has led to an increased EERE interest in developing more energy efficient semiconductor devices. U.S. leadership in manufacturing and deploying these devices can lead to a reshoring of semiconductor manufacturing foundries spurring domestic job creation, increasing productivity and competitiveness of the U.S. manufacturing industry, and combatting the climate crisis through reduced energy consumption across all sectors that utilize semiconductor technology. Other Biden Administration carbon goals that drive semiconductor efficiency R&D include goals for a zero-carbon grid by 2035 and the overall goal of a net zero carbon economy by 2050. These goals all increase the urgency of deploying decarbonization technologies such as extreme energy efficiency, massive electrification, and increased digitalization that increase use of semiconductors.

From her first day in office, Secretary Granholm has emphasized DOE's role to make scientific breakthroughs, turn them into technologies, and deploy the technologies in a way that creates good-paying jobs, ensures racial justice, and encourages collaboration. AMO's Assistant Secretary repeated these themes when she gave a keynote talk at this workshop where she discussed flattening the curve of semiconductor energy use to addressing the climate crisis. She also talked about the potential for increasing good-paying jobs by bringing semiconductor manufacturing back to the United States, the need for encouraging collaboration across the government, and the need to involve disadvantaged communities.

### **Workshop Motivation**

Semiconductor industry products power nearly every aspect of our lives, and their use is expected to continue to grow exponentially with the rapid digitalization of our modern economy in a post-pandemic world. Large industries such as telecommunications, the Internet of Things (IoT), and manufacturing are integrating more and more advanced semiconductor products into their products and processes. At the same time, Moore's Law efficiency increases due to device miniaturization have reached their physical limits. Due to these trends, semiconductor energy use is on track to become a major fraction of planetary energy use. As shown in Figure 2, computational energy use has doubled nearly every three years since 2010 (SRC 2021) and the doubling time may continue to shorten. For example, semiconductor energy use is already the dominant source of carbon emissions for research itself in major areas supported by DOE (Feder 2021). Specific semiconductor technology applications (e.g., bitcoin mining <sup>2</sup>, artificial intelligence<sup>3</sup>) show even faster doubling times so that energy use from semiconductors could become a major source of GHG pollution before the electricity grid reaches net zero carbon emissions. Without significant investments in energy efficiency for semiconductors, they could add another 20% to electricity demand by 2035 (SRC 2021). Ultra-energy-efficient semiconductor devices and architectures commercialized before 2030 could help curb this unsustainable use of electricity.

<sup>&</sup>lt;sup>2</sup> A New York Times analysis (Huang, 2021) showed that bitcoin mining energy use is now doubling every year

<sup>&</sup>lt;sup>3</sup> Mehonic and Kenyon, 2021, shows leading artificial intelligence programs doubling energy use every 2 months.

Figure 2: At current growth rates of computational energy use, the "Market Dynamics Limit" will be reached by 2035, limiting the world's computing capacity and economic growth. Alternatively, prioritizing ultra-high energy efficiency in semiconductor products can achieve an 'ultra-energy-efficiency' trajectory in which computing/economic growth and energy use are decoupled.

Figure 2 shows that ultra-energy-efficient devices and the end-use products into which they are incorporated must be drastically more energy efficient ("ultra-energy-efficiency path") to flatten the curve of semiconductor energy use. UPM processes, tools, and metrology will provide the necessary manufacturing innovations necessary to enable these ultra-efficient devices. Addressing challenges and exploring opportunities in these separate but interconnected topics can provide the best path forward to drastically reduce semiconductor energy use.

The looming semiconductor energy impact also comes at a time when the Biden-Harris Administration is accelerating the U.S. response to the climate crisis. The nation is at an inflection point where federal investment in joint R&D for semiconductors—including the underlying manufacturing technologies for the next generation of devices—could accelerate our transition toward a sustainable path that avoids planetary energy impacts, while revitalizing a key domestic industry that offers high-paying jobs.

By partnering with U.S. industry to further develop UPM technologies, AMO hopes to increase the competitiveness of domestic device and chip manufacturing, spur domestic job creation in this growing field, and combat the climate crisis by flattening the curve of semiconductor energy consumption across all sectors that use semiconductors by 2030.

AMO began its atomically precise manufacturing program in 2015 based on the hypothesis that increasing control at the atomic scale yields greater energy efficiency. As manufacturing technology has become more advanced, manufacturing precision has similarly developed, from the millimeter scale to the sub-nanometer scale. Projects within the program address critical needs in devices, UPM processes, and UPM tools, the three technical topics of the workshop. The workshop aimed to identify emerging ultra-energy-efficient devices and UPM processes and tools, critical challenges, and key R&D opportunities to further expand and grow AMO's semiconductor R&D efforts with particular focus on energy efficiency.

#### **Workshop Overview**

To better understand the challenges and opportunities in developing ultra-energy-efficient devices and their enabling manufacturing and metrology technologies and AMO's role in this area, DOE held the Workshop on

Ultra Precision Control for Ultra-efficient Devices on April 21–23, 2021. Representatives from industry, academia, the DOE national laboratories, and non-governmental organizations gathered virtually to hear presentations and participate in panel discussions with subject matter experts, as well as contribute to topical facilitated discussions/brainstorming sessions. The workshop was divided between three technical topics: ultra-efficient devices, UPM processes, and UPM tools and metrology. This workshop report summarizes the attendees' input on the emerging technologies and RDD&D challenges and opportunities for the three technical workshop topics from the presentations, panels, and facilitated discussions.

Below is a brief overview of the workshop agenda. More detailed summaries of all of the talks are included in Appendix B.

On the first day of the workshop, participants learned about the growing semiconductor energy crisis, the emerging semiconductor devices that will help address this problem, and the Biden Administration and U.S. industry priorities that such research would support. Plenary talks featured speakers from DOE and the Semiconductor Research Corporation (SRC). The first panel session included representatives from different government agencies on their semiconductor R&D efforts broadly. Next, a keynote from SRC focused on prospects for energy efficiency and paths forward to address the growing semiconductor energy crisis. The day concluded with a panel and facilitated discussion on ultra-energy-efficient devices.

The second day began with an interactive talk about the motivation for dividing the workshop into devices, processes, and metrology as well as a discussion of another recent workshop focused on atomic precision. The workshop then moved onto panel discussions. The first focused on UPM processes and included a talk from one of AMO's current projects followed by extensive Q&A. The next panel focused on UPM tools and metrology and also included a talk from an AMO sponsored project. Both panel sessions were followed by a facilitated discussion.

The third and final day summarized the findings of Day 1 and Day 2 with an extensive report-out session covering the three technical topics and a discussion on priority research directions. The workshop concluded with a talk discussing historical and future trends of computing and other elements (e.g., architecture) needed to achieve sustainable computing.

Each of the workshop sessions, including the three technical topics, are summarized below.

## **Opening Plenary Session**

The opening plenary and panel speakers clarified the strong alignment of AMO, EERE, DOE, and the federal government's RDD&D goals with the goals of the semiconductor industry. For example, on Day 1, Tina Kaarsberg, chair of the workshop series, noted that AMO's second goal for increased lifecycle and materials efficiency of manufactured products is supported by numerous specific goals in SRC's decadal plan, especially its fifth grand goal to discover computing paradigms/architectures with a radically new computing trajectory, demonstrating >1,000,000x improvement in energy efficiency.

The government keynote speech by EERE's Acting Assistant Secretary, Kelly Speakes-Backman, also strongly emphasized the DOE and semiconductor industry's common cause for increasing energy efficiency and warned that without dramatic improvements in device and computing system efficiency, semiconductors could shift from being a climate solution to a climate problem, as shown in Figure 2. She also noted that investments in manufacturing RDD&D for ultra-energy-efficient semiconductor devices can bolster the domestic semiconductor manufacturing industry by increasing its competitiveness and size, and expanding the well-paid workforce. She noted this was one key reason that the Administration's American Jobs Plan called for \$50 billion in semiconductor manufacturing and research at DOE and other agencies.

The industry keynote by SRC Chairman and President Todd Younkin echoed Acting Assistant Secretary Speakes-Backman's remarks about the need for energy efficiency and increased investments in semiconductor manufacturing and workforce. He, and several speakers that followed, also provided numerous examples of research, demonstration, and deployment efforts needed for co-design of new energy efficient systems up and down the stack; advanced metrology; manufacturing R&D for materials and processes; and joint, basic applied research in physics, materials, and chemistry. All plenary speakers and the government panel emphasized the need for industry government partnerships and access to advanced facilities. Details on these presentations can be found in the speaker summaries in Appendix B. Multiple plenary and panel speakers emphasized the following themes:

- The need for semiconductor ultra-energy efficiency in a decade.

- The potential to accelerate the growth of the domestic high-tech workforce through RDD&D investments in the semiconductor industry.

- The importance of RDD&D investments in the following priority research areas, for the development of ultra-energy-efficient semiconductor devices:

- Co-design

- Processes

- Materials

- Chemistry

- Metrology.

After the plenary talks and the Federal Panel summarizing the federal semiconductor R&D ecosystem, came the panel session and facilitated discussion for each of the technical topics, Ultra-efficient Devices, Ultra Precise Manufacturing Processes, and Ultra Precise Manufacturing Tools and Metrology. Each are summarized below. This report also includes a fourth section, Cross Cutting Issues, that summarizes the crosscutting topics that were identified across the three technical topics.

## **Ultra-Energy-Efficient Devices**

The metal-oxide-semiconductor field-effect transistor (MOSFET)—the basis for today's logic, memory, and radio frequency (RF) device architectures—is reaching its fundamental thermodynamic limit for switching. MOSFETs' diminishing improvements in energy efficiency can no longer offset the energy consumption associated with their exponentially increasing use. As detailed in the read-ahead <u>document</u>, many new devices utilizing new materials (including engineered materials) and device physics that can exceed current MOSFET-based devices in energy efficiency are being explored. AMO is most interested in those that have the potential to be commercialized by 2030. As a result, the Device panel's presentations and discussions were focused on those with potential to be integrated with today's complementary metal-oxide semiconductor (CMOS) fabrication lines.

The Devices session began with a plenary talk by Victor Zhirnov, chief scientist of SRC, discussing the current trajectory of computational energy use and the thermodynamic parameters that need to increase to reduce energy consumption by orders of magnitude. He also discussed how the energy consumption of device types had changed over time, Figure 3. A panel session focusing on emerging ultra-efficient logic, memory, and RF/communications devices that could be commercial by 2030 followed. Note that the categories of devices are not mutually exclusive.

Figure 3: Relative energy consumption of logic, memory, and interconnects in 1990 and 2021. With Moore's Law and other improvements—such as new materials and device architectures—primarily directed at logic devices, energy consumption of memory and interconnects outpaced that of logic. Source: Zhirnov, V., 2021

Panelist Alan Seabaugh (University of Notre Dame) discussed the pros and cons of two promising, ultraefficient logic devices, tunneling field-effect transistors (TFET) and ferroelectric field-effect transistors (FeFET); Dmitri Nikonov (Intel) discussed the magnetoelectric spin-orbit (MESO) as a logic device; Carlos H. Diaz (TSMC) provided an overview of promising, ultra-efficient memory devices and the critical parameters of interest; and finally, David Howard discussed TowerJazz's history and capabilities in RF electronics. A vigorous Q&A session followed the panel talks. Key concepts and takeaways discussed during the Devices plenary talk, panel session, and facilitated discussions are discussed in the following sections. A more detailed summary of the plenary talk and each panel speakers can be found in Appendix B. Table 1, at the end of the Devices chapter summarizes participant input from the facilitated session identifying the most common device parameters that may suffer when maximizing for energy efficiency and R&D challenges and opportunity areas. Table C-1 to Table C-3 includes the full participant input.

### Near-term Emerging Ultra-energy-efficient Devices

As shown in Figure 1, device markets are generally divided according to their function. Underlying these functions in the near term are three primary device types: logic, memory, and RF.

#### **Ultra-energy-efficient Logic Devices**

AMO is already conducting ultra-precision manufacturing research supporting 7 of the top 14 logic devices identified in the International Roadmap for Devices and Systems (IRDS): 2020 Edition. Emerging logic devices can be conceptually divided according to their switching mechanism: electric charge, magnetism/spin, or other "state variables."<sup>4</sup> Several new devices, however, use more than one mechanism. According to the IRDS (2020), these logic device challenges include the need for:

- Full interface control and a bandgap (e.g., TFETs, graphene).

- Synthesis (e.g., carbon nanotubes [CNTs]) with tight distribution of bandgap and mobility.

- Low defect density (e.g., complex metal oxides).

- Low-resistance ohmic contacts (e.g., high-mobility transition metal dichalcogenides).

Summarized below are logic devices with improved energy efficiency that were discussed during the workshop:

**Tunnel Field-Effect Transistors (TFET):** Transistors based on quantum tunneling rather than thermionic emission have been shown to operate at 1/10 the power of leading-edge conventional transistors (MOSFET) (with switching energy as low as  $2x10^{-18}$  Joules, or 2 attojoules). TFET's low subthreshold swing (SS) of less than 60 mV/decade enables lower system power. TFETs' requirement for atomic precision, due to quantum tunneling that is exponentially dependent on the tunnel barrier thickness, is a scale-up challenge. As shown in Figure 4, TFET's current has been too low at higher voltages to serve as a drop-in replacement for conventional CMOS. Fabrication requirements (e.g., high temperature) for atomic precision prevent ready

Figure 4: All TFETs exceed the 60 mV/decade upper limit slope of MOSFET (Avci, Morris, and Young 2015).

integration of TFET into CMOS, but manufacturing research (described in the next section) is underway to overcome these challenges.

**Spin-Based Logic:** MESO devices combine magnetization and polarization in one switch and have the potential to achieve attojoule-class logic gates for computing. MESO logic has collective switching, strong thresholding behavior, and nonvolatility (Manipatruni, Nikonov, and Young 2018). The optimal combination of these two variables keeps the operating voltage, and hence the energy consumption of the device, low. Although these devices are slower than traditional logic devices, speed may not be important when a small energy footprint is desired. However, the wide array of novel materials and layering schemes needed for MESO devices could present manufacturing challenges.

Summarized below are two additional devices that weren't discussed during the workshop but show potential to drastically reduce energy consumption of logic devices.

**Carbon Nanomaterials:** CNTs' switching energy can be as low as 100 attojoules, two orders of magnitude lower than that of state-of-the-art transistors. But growing defect-free aligned CNTs require atomic-level control. Graphene was the first 2D material used for transistors but its lack of bandgap limits its utility for digital.

<sup>&</sup>lt;sup>4</sup> State variables refer to the carrier for logic operations.

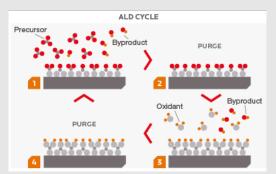

**2D** Channel FET: Non-carbon 2D materials, such as transition metal dichalcogenides, are proving to be more promising candidates than graphene for low-energy switching for future devices, as non-carbon materials provide improved electrostatic control and carrier mobility in some materials (Lu and Seabaugh, 2014; Hartmann et al. 2021). Advances in selective atomic layer deposition (ALD), atomic layer etching (ALE), area-selective deposition (ASD) are needed to accelerate commercialization.

#### **Ultra-energy-efficient Memory Devices**

As with logic devices, novel channel materials or device physics can be leveraged for ultra-energy-efficient memory devices. AMO's ultra-precision manufacturing R&D portfolio supports four of the top nine memory devices identified in the IRDS. As with logic devices, there are charge- and non-charge-based devices. AMO determined from literature searches where comparative data are available that FeFET and phase change memory (PCM) are among the most promising memory technologies for improved energy efficiency. Spin transfer torque (STT) and ferroelectric random-access memory (FeRAM) devices, two ultra-energy-efficient memory devices, have already been commercialized.<sup>5</sup> According to the IRDS (2020), long-term challenges for these memory devices include:

- Control of oxygen vacancy formation at metal interfaces and interactions of electrodes with oxygen and vacancies (e.g., complex oxides).

- Needs for long-term reliability of the switching mechanism.

- Improvements in switching speed and cyclic endurance.

- Uniformity of the switching bias voltage and resistance, both for the on state and the off state (e.g., conductive bridge RAM, PCM).

FeFET, the most energy-efficient memory device, requires less than 1 femtojoule (10<sup>-15</sup>J) per bit, while FeRAM and PCM require 50fJ/bit and 3pJ/bit, respectively. For comparison, traditional magnetoresistive random access memory (MRAM), resistive random-access memory (RRAM), and NAND Flash memories require 2pJ/bit, 50pJ/bit, and 1nJ/bit, respectively. The most energy efficient emerging memory devices discussed during the workshop, which still face significant barriers before commercialization, are summarized below:

**FeFET**: FeFET incorporates a ferroelectric oxide between the channel and gate electrode. The permanent polarization of the ferroelectric material enables its memory capabilities. The 2011 discovery of advanced CMOS-compatible HfO<sub>2</sub>-based ferroelectric devices mean that FeFET made from HfO<sub>2</sub> thin films can be used both as non-volatile memory elements and as logic compute elements (Khan, Keshavarzi, and Datta 2020). Hence, FeFETs are likely to be used for non-traditional, in-memory (e.g., neuromorphic) computing data-flow architectures to enable small, energy-efficient systems needed for edge computing (e.g., IoT). Most of FeFET's low energy use is not due to the device itself (which uses more energy than non-STT spintronics device) but to the close physical proximity of memory and logic in the same FeFET device, which avoids energy-intensive data movement. Current manufacturing challenges include improved interface control of the gate stack and polarization hysteresis.

**Phase Change Memory (PCM)**: PCMs are a type of resistance-based memory. These rely on resistance-based read operation of a passive memory device and have high-speed read/write operation (10 ns), ultra-scalability below 10 nm, and compatibility with state-of-the-art CMOS processes. In particular, PCM utilizes changes in conductance caused by changes in a material's crystal structure (crystalline to amorphous), due to thermal input, to achieve memory function. PCMs that can be switched by non-thermal phase changes are also being investigated. Because of the inability of current to flow in the amorphous state, PCM's have negligible leakage and thus promise ultra-low energy consumption and very long memory retention and stability (Le Gallo and

<sup>&</sup>lt;sup>5</sup> STT MRAM has entered commercial production under the name Everspin at major foundries across the world.

Sebastian 2020). Integration of non-standard materials into current CMOS process flows will be a key challenge in commercialization efforts.

#### Ultra-Energy-Efficient Radio Frequency (RF)<sup>6</sup> Devices

RF devices and circuits are widely deployed in telecommunication systems. Unlike emerging logic and memory devices, novel, energy efficient RF devices do not leverage new physical phenomena for switching as their operating parameters are not near fundamental physical limits. Still, many new materials are being explored to increase the performance and decrease the energy use of RF devices. The major opportunity and challenge for improving energy efficiency of telecommunication systems are in the devices found in base stations (i.e., communication towers) including transceivers, power amplifiers, and antennas, where 5G networks will require an estimated quadrupling of power, if the technology is not improved.<sup>7</sup>

Today's technology is based on Gallium Arsenide (GaAs), the material of choice for RF since the 1970s, thanks to its high resistivity. High saturation velocity, carrier mobility, and larger bandgap make GaAs more energy efficient than silicon-based RF components. Its mature product lines at large fabrication facilities still make it the go-to material for large-scale monolithic microwave integrated circuit (MMIC) production (Benson 2017). Unlike emerging logic and memory devices that leverage different state variables, emerging RF devices rely on novel materials such that materials processing and growth constitute the main barriers to their widespread commercialization. Summarized below are two materials for emerging RF devices that were prominently discussed during the workshop.

Figure 5: GaN is able to operate at significantly higher power at similar frequencies compared with traditional GaAs and SiGe technology (Benson 2017).

**Gallium Nitride**: Gallium nitride is an attractive alternative to standard GaAs MMICs because of its higher output power at microwave frequencies and higher operating temperatures and voltages. Faster switching speeds, lower resistance when switching to the "on" state, and higher thermal conductivity make GaN-based RF devices more energy efficient than either GaAs or silicon, Figure 5. Defect-free growth of GaN on native or nonnative substrates, however, has proven to be a barrier in transitioning from traditional GaAs or SiGe RF devices to GaN based devices according to workshop attendees.

**Carbon Nanotubes (CNTs)**: CNTs' one-dimensional geometry has inherent linearity, which leads to a high dynamic range. This makes CNT-based devices well suited to electromagnetically noisy environments. In addition, CNT's high carrier mobility, high saturation velocity, and

ballistic transport allow for extremely low power operation for CNT circuits. Growing or depositing pristine CNTs with tight diameter control and semiconducting-to-metallic CNT selectivity has presented challenges in fabricating CNT devices at manufacturing-relevant CNT density, current density, and transconductance. Hence CNT device properties still fall short of their theoretical performance values.

<sup>&</sup>lt;sup>6</sup> Radio frequency devices typically operate between 20 kHz and 300 GHz.

<sup>&</sup>lt;sup>7</sup> Deploying ultra-energy efficient devices that reduce power consumption in edge devices that rely on wireless communication (e.g., mobile phones, smart watches, and laptops) improve battery life, device lifetime, and mean time to failure, however energy efficiency improvements in these areas are not hitting the same limits of operation as for logic and memory that require enhanced innovation.

### Challenges and R&D Opportunities for Ultra-Efficient Devices

There is precedent for energy efficiency to take priority over other performance metrics. As was mentioned during the panel session, this tradeoff was accepted when transitioning from bipolar junction transistors (BJT) to CMOS devices as the primary device in integrated circuits (ICs). Although BJTs exhibited faster switching speeds, CMOS devices ultimately prevailed due to their higher energy efficiency. Industry made a concerted effort to transition to CMOS devices and subsequently developed the necessary infrastructure to support CMOS manufacturing. Similarly, to transition to the aforementioned ultra-energy-efficient technologies, the semiconductor industry again must be aligned and exert a concerted effort towards this change in the coming decade.

However, in developing emerging devices, it is clear that industry must be guided by a holistic set of metrics, not just energy efficiency, and the expectation would be that the non-energy-efficiency performance metrics would be comparable to that of today's devices.

During the Devices session, numerous challenges and R&D opportunities were discussed, summarized below.

**Material and interface quality**: Semiconductor material quality is critical for proper device functioning. State-of-the-art semiconductor devices now approach atomic scales where materials behave differently than at the bulk scale. Hence references that were historically used in processing, such as material constants and phase-change behavior, have ceased to be applicable. In addition, interfacial quality has become critical, since even a single defect or impurity atom at an interface can drastically alter device performance. Going forward, doping profiles, contacts, and dielectrics will all require pristine interfacial quality—or engineered materials without such interfaces—to achieve theoretical device performance. Atomically precise control has become increasingly important as devices continue to shrink.

**Material synthesis**: Emerging devices that rely on non-Si materials, such as CNTs, graphene nano-ribbons, other 2D material systems, GaN, etc. often require pristine material growth to achieve theoretical performance targets and to exceed incumbent technology. Consistent, controllable growth that is cost effective is still a challenge to some extent for all non-Si materials. In addition, even processes that show consistent growth at the benchtop scale typically face significant challenges in scale up. Computational fluid dynamics modeling may be a necessity to adequately transition to high volume process chambers typically found in fabs. In addition, development of in-situ characterization was highlighted as a promising path forward in improving synthesis and growth of novel materials. On the other hand, leveraging engineered materials was discussed as an alternative to using non-traditional materials. Advances in atomic manipulation open the door for conventional materials to take on unconventional properties. Not only do these materials avoid novel, complex material growth and synthesis processes, they also have mature, established supply chains.

**Material and mechanical stability**: Many emerging devices use novel materials that have unknown long term operational stability. Especially in emerging memory devices, cycling may have profound impact on endurance and hysteresis not commonly found in conventional memory devices. As feature sizes decrease, some of these ultra-precise structures may not be robust to the operating currents or voltages of the devices they are intended to replace. In general, novel or non-standard materials may present significant process integration challenges including but not limited to mechanical integrity and thermal stability of the structures and material interfaces, and operational stability issues that may not have been anticipated during early-stage device research. Results presented at the workshop, however, showed that atomically precise structures, such as abrupt doping profiles, proved to be more robust to thermal cycling than conventional CMOS with which they were integrated despite their limited thermal budgets.

**Material scarcity**: Noble metals have long been the cornerstone for low-contact-resistance materials and their increasing scarcity has become a growing concern. Process materials—those that are not part of the final product, such as hydrofluoric acid and helium—are becoming increasingly scarce as well. In addition,

feedstocks for Si substrates themselves are becoming scarcer as competition for these materials increases, both within the electronics industry and from other industries such as the photovoltaic and display industries.<sup>8</sup>

**Contamination**: A large number of emerging, ultra-efficient devices rely on novel materials that are not typically found in CMOS fabrication lines. There are significant contamination concerns when introducing new materials into an established fabrication environment. Plasma processing, harsh chemicals, and even air may adsorb chemicals or damage the surface resulting in poor device performance. These materials may adsorb to chamber walls or equipment surfaces and inadvertently deposit on other wafers that use the same tools. These foreign particles may act as mobile ions or charge traps resulting in poor device yield. Although a device may show promise on the R&D level, its adoption at the manufacturing level will require stringent material contamination control to ensure that current process flows are not affected.

**Modeling**: Modeling of novel devices was stressed to be critically important to understand device performance and its circuit and system level impact. As emerging device rely on atomic-scale interactions, physics-based modeling and understanding of quantum effects and their impact on device performance will be crucial. These quantum effects, coupled with novel material properties, will require the development of new models to predict performance and inform robust circuit designs as well as assess system-level performance benefits of the innovative devices and processes being explored. The development of a multi-scale model that incorporates phenomena at the atomic level to the circuit level with the capability of feeding into traditional design tools was raised as a powerful method in developing next generation devices. AI/ML techniques are useful when plentiful experimental and/or simulation data is available.

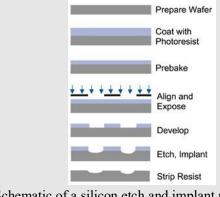

**Process Development**: Process development, especially advances in patterning, was identified as a critical R&D pathway to enable ultra-efficient devices. As emerging devices become more complex in design and material combinations, alignment and pattern-transfer processes will need improved accuracy, precision, and repeatability. Bottom-up fabrication techniques including self-limiting and self-assembling chemical processes were cited as the most scalable approaches to atomic precision, although slower and less scalable techniques may be required to direct the self-assembly process. Area Selective Deposition (ASD) in particular was viewed as a key bottom-up area needing progress.

As was mentioned in the UPM Processes panel session, integration of novel processes or tools in the process flow may require changing several steps prior to and after the step of interest or completely changing a process module. For example, the integration of ALD of high- $\kappa$  dielectrics not only required changing deposition tools (from chemical vapor deposition (CVD) to ALD) but also required changes in previous steps for surface preparation and changes in steps after deposition. In this way, the manufacture of emerging devices may significantly alter current very large-scale integration (VLSI) processes and facilities.

**Understanding Device Failure**: Manufacturability of these emerging devices will ultimately decide whether these devices make it past the R&D phase. Evaluating the degradation mechanisms of emerging devices will provide useful insight into HOW these devices fail. These emerging devices have not been manufactured at scale, so the failure modes have not all been identified, creating a large knowledge gap in failure analysis. With knowledge of the most common failure modes, the manufacturability of these devices can be further improved. Similarly, accelerated lifecycle testing can be done to evaluate the stability of these devices. If significant yield loss is observed during traditional lifecycle testing, then device stability would be identified as a primary concern.

**System level Considerations**: Ultra-energy-efficient devices will only be widely deployed if they can be integrated into larger systems while retaining their energy efficiency. System level integration, such as advanced packaging and assembly, high-speed interconnects, and system architecture, should be designed to

<sup>&</sup>lt;sup>8</sup> According to the SRC Decadal Plan, page 43, at its current pace, the demand for memory, roughly 10<sup>26</sup> bits by 2040, will exceed the projected global silicon supply by roughly 3 orders of magnitude.

maximize the benefit of ultra-energy-efficient devices. Only those ultra-energy-efficient devices that prove to translate to system-level ultra-energy efficiency will be commercialized.

| Table 1: Participant Input on Ultra-energy-efficient Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Emerging Ultra Efficient Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Performance Metric Tradeoffs                                                                                                                                                                                           |  |  |